Dinamički RAM

| Tipovi računarske memorije |

|---|

| Promenljiva |

| RAM |

| U razvoju |

| Istorija |

|

| Nepromenljiva |

| ROM |

| NVRAM |

| Ranije faze NVRAM |

| Mehanička |

| U razvoju |

| Istorija |

|

Dinamički RAM (engl. dynamic RAM (dynamic random-access memory — „dinamička memorija sa slučajnim pristupom“)) ili skraćeno DRAM, je tip RAM memorije koja čuva svaki bit podataka u posebnom kondenzatoru u okviru integrisanog kola. Kondenzator može biti pun ili prazan; ova dva stanja predstavljaju dve vrednosti bita, uobičajeno se zovu 0 i 1. Pošto kondenzatorima curi naboj, informacija bi na kraju nestala ako se ne bi kondenzator periodično osvežavao. Zbog ovih zahteva za osvežavanje, dinamička memorija je suprotna u odnosu na SRAM i druge statičke memorije.

Glavna memorija („RAM“) u ličnim računarima je dinamički RAM (DRAM). To je RAM u stonim računarima, laptopovima i radnim stanicama računara, kao i nekim RAM konzolama za video igre.

Prednost DRAM-a je njogova jednostavna struktura: samo jedan tranzistor i jedan kondenzator su potrebni po bitu, u poređenju sa 4 ili 6 tranzistora u SRAM-u. Ovo omogućava DRAM-u da postigne veliku gustinu. Za razliku od fleš memorija, DRAM je promenljiva memorija (naspram nepromenljive memorije), pošto gubi podatke brzo nakon prestanka napajanja. Tranzistori i kondenzatori koji se koriste su veoma mali; bilioni mogu da stanu na jedan memorijski čip.

Istorija

[uredi | uredi izvor]Kriptoalanitička mašina pod kodnim nazivom Aquarius („Vodolija“) korišćena je u Bletchley Park za vreme Drugo svetsko rata sa ugrađenom čvrsto-žičanom dinamičkom memorijom. Papir traka je pročitana i znakovi na njoj „su zapamćeni u dinamičkom skladištu ... Skladište koristi veliku banku kondenzatora, koji su napunjeni ili ne, napunjeni kondenzator predstavlja krst (1) a prazni kondenzator tačku (0). Pošto napunjeni kondenzatori postepeno cure, periodični puls se primenjuje da napuni one koji su još uvek puni (otuda termin „dinamički“)“.[1]

Godine 1960. Arnold Farber i Judžin Šlig, radeći za IBM, stvorili su čvrsto-ožičenu memorijsku ćeliju, korišćenjem tranzistor kapija i tunel diodu leča (u elektronici to je kolo koje se koristi za skladištenje informacija). Zamenili su leč sa dva tranzistora i dva otpornika, a konfiguracija je postala poznata kao Farber-Schlig ćelija. Godine 1965. Benjamin Agusta i njegov tim sa IBM-a svorio je 16-bitni silikonski memorijski čip zasnovan na Farber-Schlig ćeliji, sa 80 tranzistora, 64 otpornika, i četiri diode. Godine 1966. DRAM je izmislio dr Robert Dennard u IBM Thomas J. Watson Research Center. Njemu je odobren U.S. patent broj 3,387,286 Arhivirano na sajtu Wayback Machine (31. decembar 2015) 1968. godine. Kondenzatori su bili korišćeni za ranije memorijske šeme poput bubnja od Atanasov-Berijevog računara, the Williams-ove cevi i Selectron cevi.

Toshiba "Toscal" BC-1411 elektronski kalkulator, koji je predstavljen u nevembru 1966. godine,[2] koristio je oblik dinamičkog RAM-a izgrađenog od diskretnih komponenti.[3]

Godine 1969. Honeywell je zatražio od Intela da napravi DRAM pomoću 3-tranzistorske ćelije koje su oni razvili. Intel ih je napravio pod nazivom Intel 1102 (1024x1) početkom 1970. godine. Međutim, 1102 je imao mnogo problema, što je navelo Intel da započne rad na sopstvenom poboljšanom dizajnu, u tajnosti da bi se izbegao sukob sa Honeywell. Ovo je postalo prva komercijalno dostupna DRAM memorija, Intel 1103 (1024x1), u oktobru 1970. godine, uprkos početnim problemima sa niskim prinosom do pete revizije masaka. 1103 je dizajnirao Joel Karp i izložila Barbara Maness.

Prvi DRAM sa višestrukim redovima i kolonama adresnih linija bio je Mostek MK4096 (4096x1) dizajniran od strane Robert Proebsting i predstavljen 1973. godine. Šeme adresiranja koriste iste adresne pinove da primi nižu polovinu i višu polovinu adrese memorijske ćelije, koja će se prebacivati između dve polovine na nezmenične cikluse magistrale. Ovo je bio radikalan napredak, efektivno je prepolovio broj potrebnih adresnih linija, što je omogućilo da stane u paket sa manje pinova, i prednost troškova koji su rasli sa svakim povećanjem veličine momorije. MK4096 se pokazao kao veoma robustan dizajn za korisničke aplikacije. Na gustini od 16K, prednost troškova se povećavala; Mostek MK4116 16K DRAM, uveden 1976. godine, ostvario je više od 75% udela svetskog DRAM tržišta. Međutim, kad je gustina porasla na 65K u ranim 90-im godinama, Mostek-a je pretekao japanski proizvođač DRAM-a, prodajući kvalitetniji DRAM koji koristi istu šemu multipleksiranja po nižoj ceni troškova. Vidi–United States relations# Frictions u industrijskom sektoru poluprovodnika.

Princip rada

[uredi | uredi izvor]

DRAM se obično raspoređuje u pravougaoni niz nabojnih ćelija za skladištenje koje se sastoje od jednog kondenzatora i tranzistora po bitu podatka. Slika sa desne strane prikazuje jednostavan primer 4h4 matrične ćelije. Moderna DRAM matrica su više hiljada ćelija u visinu i širinu.

Duge hirizontalne linije koje povezuju svaki red poznate su kao reč linije. Svaka kolona ćelija se sastoji od dve bit-linije, svaka povezana sa svakom drugom ćelijom za skladištenje u koloni (ilustracija sa desne strane ne uključuje ovaj važan detalj). One su opšte poznate kao + i – bit-linije.

Operacije čitanja bita podataka sa DRAM skladišne ćelije

[uredi | uredi izvor]- Sense amplifier je isključen. (U modernoj memoriji računara, sense amplifier je jedan od elemenata koji čine kola na poluprovodničkom memorijskom čipu (integrisano kolo)).

- Bit-linije su napunjene do tačno jednakih napona koji su između visokih i niskih logičkih nivoa (nap. 0.5V ako su dva nivoa 0 i 1V). Bit-linije su fizički simetrične da bi zadržale jednaku kapacitivnost, pa stoga u tom trenutku njihovi naponi su jednaki.

- Prethodnog naelektrisanja kola se isključuju. Zato što su bit-linije relativno dugačke, one imaju dovoljno kapacitivnosti da održe napon kratko vreme. Ovo je primer dinamičke logike.

- Željeni redna reč-linija je tada prešla na visok nivo da se poveže sa ćelijom kapacitatora za skladištenje sa svojom bit-linijom. Ovo izaziva da tranzistor provodi, prenosi naelektrisanje iz skladišne ćelije do povezane bit-linije (ako je uskladištena vrednost 1) ili od povezane bit-linije di skladišne ćelije (ako je uskladištena vrednost 0). Pošto je kapacitivnost bit-linije mnogo veća od kapacitivnost ćelije za skladištenje, napon na bit-liniji se vrlo malo povećava ako je kondenzator ćelije za skladište prazan i malo se smanjuje ukoliko je kondenzator ćelije za skladištenje napunjen (npr. 0.54V i 0.45V u dva slučaja). Pošto druge bit-linije održavaju 0.50 V postoji mala razlika napona između dve uvrnute bit-linije.

- Sense amplifier je da su sada povezani sa parovima bit-linija. Pozitivni povratak nastaje između unakrsno povezanih invertora, na taj način se pojačava razlika napona između parnih i neparnih redova bit-linija određene kolone sve dok jedna bit-linija ne bude u potpunosti na najnižem nivou, a druga na maksimalno visokom naponu. Kada se to desi, red je „otvoren“ (podaci željene ćelije su na raspolaganju).

- Sve ćelije za skladištenje na otvorenom redu su istovremeno osetljive, i sense amplifier izlazi lečovan. Kolona adrese onda bira koji leč bit da poveže na eksternu magistralu podataka. Čitanje iz različitih kolona u istom redu može da se izvrši bez odlaganja otvaranja reda, zato što su za otvoreni red, svi podaci već bili osetljivi i lečovani.

- Dok se dešava čitanje kolone u otvorenom redu, struja teče unazad na bit-linijama iz izlaza sense amplifier-a i ponovo puni ćelije za skladištenje. Ovo pojačava (tj. „osvežava") punjenje u ćeliji za skladištenje povećanjem napona u kondenzatoru za skladištenje ako je bio na početku napunjen, ili ga drži nenapunjenim ako je bio prazan. Treba imati na umu da, zbog dužine bit-linija, postoji prilično dugo širenje kašnjenja punjenja da bude prebačeno natrag na ćeliju kondenzatora. Ovo traži značajno vreme za sense amplifier, i tako se preklapa sa jednom ili više kolona za čitanje.

- Kada završi sa čitanjem svih kolona u tekućem otvorenom redu, reč-linija se isključuje diskonekcijom ćelija kondenzatora za skladištenje (red „zatvoren") sa bit-linije. Sense amplifier je isključen, a bit-linije se ponovo pune.

Za pisanje u memoriju

[uredi | uredi izvor]Za skladištenje podataka, red je otvoren i data kolonsko osećanje pojačavača, je privremeno primorano da zahteva visoko ili nisko naponsko stanje, uzrokujući da bit-linija puni ili prazni ćeliju kondenzatora za skladištenje do željene vrednosti. Zbog osetljivog pojačivača pozitivna povratna konfiguracija, će održati bit-liniju na stabilnom naponu i posle prestanka napona. Tokom pisanja na određenu ćeliju, sve kolone u redu su istovremeno osetljive samo tokom čitanja, tako da ikao jedna skladišna ćelija kapacitatora menja stanje, ceo red se osvežava (napisan ponovo), kao što je prokazano na slici desno.

Brzina osvežavanja

[uredi | uredi izvor]Tipično, proizvođač precizira da svaki red mora imati svoje ćelije kondenzatora za skladištenje osvežene svakih 65ms ili manje, kao što je definisao JEDEC (Foundation for developing Semiconductor Standards) standard. Logika osveženja je obezbeđena u DRAM kontroleru koji automatizuje periodično osvežavanje, to jest to ne moraju da izvršavaju softver ili drugi hardver. Ovo čini logiku kola kontrolera komplikovanom, ali ta mana je opravdana činjenicom da je DRAM mnogo jeftiniji po ćeliji za skladištenje i pošto je svaka ćelija za skladištenje jednostavna, DRAM ima mnogo veći kapacitet po jedinici površine nego SRAM.

Neki sistemi osvežavaju svaki red u rafalu aktivnosti koje uključuju sve redove svakih 64ms. Drugi sistemi osvežavaju jedan red u trenutku koji se rasporedi u intervalu od 64ms. Na primer, sistem sa 213 = 8192 redova bi zahtevao raspoređeno osvežavanje jednog reda svakih 7.5µs što je 64ms podeljeno na 8192 redova. Nekoliko sistema u realnom vremenu osvežava deo memorije u vremenu koje je određeno pomoću spoljne tajmer funkcije koja reguliše rad ostatka sistema, kao što je vertikalna praznina koja se javlja svakih 10-20ms u video opremi. Sve metode zahtevaju neku vrstu brojača da prati koji sledeći red treba da se osveži. Većina DRAM čipova uključuje brojač. Stariji tipovi su zahtevali eksternu logiku osvežavanja za držanje brojača.

Pod određenim uslovima, većina podataka u DRAM-u može se povratiti čak i ako DRAM nije bio osvežen nekoliko minuta.

Tajming memorije

[uredi | uredi izvor]Mnogi parametri su potrebni da se u potpunosti opiše tajming DRAM operacija. Evo nekih primera za dva vremenska razreda sinhronog DRAM-a, sa liste sa podacima objavljenim 1998. godine:[4]

| "50 ns" | "60 ns" | Opis | |

|---|---|---|---|

| tRC | 84 ns | 104 ns | Nasumično vreme ciklusa čitanja i pisanja (od jednog punog/RAS cilusa do drugog) |

| tRAC | 50 ns | 60 ns | Vreme pristupa: /RAS nizak do izvan validnih podataka |

| tRCD | 11 ns | 14 ns | /RAS nizak u /CAS nisko vreme |

| tRAS | 50 ns | 60 ns | /RAS pulsirajuća širina (minimalan/RAS nisko vreme) |

| tRP | 30 ns | 40 ns | /RAS vreme prethodnog punjenja (minimalan/RAS visoko vreme) |

| tPC | 20 ns | 25 ns | Ciklus vremena strana-režim čitati ili pisati (/CAS do /CAS) |

| tAA | 25 ns | 30 ns | Vreme pristupa: Validne adrese kolona do validnih podataka van (uključuje adresno podešavanje vremena pre / CAS nizak) |

| tCAC | 13 ns | 15 ns | Vreme pristupa: / CAS nisko do validnih podataka van |

| tCAS | 8 ns | 10 ns | /CAS niska pulsirajuća širina minimalna |

Dakle, generalno citirano broj je /RAS vreme pristupa. Ovo je vreme koje je potrebno da se pročita nasumični bit iz prethodno napunjenog DRAM niza. Vreme da se pročita dodatni bit iz otvorene stranice je mnogo manji.

Kada takav RAM pristupi logici generatora takta, vremena se generalno zaokružuju u najbližem ciklusu. Na primer, kada se pristupa od strane mašine sa 100 MHz (npr. 10ns ciklu), 50ns DRAM može da izvrši prvo čitanje u pet ciklusa genaratora takta, a dodatno čitanje u oviru iste strane na svaka dva ciklusa generatora takta. Ovo se obično opisuje kao "5-2-2-2" tajming, kao rafal od četiri čitanja unutar strane koje su uobičajene.

Kad se opisuje sinhrona memorija, tajming je opisan kao ciklus generatora takta odvojen crticom. Ovi brojevi predstavljaju tCL‐tRCD‐tRP‐tRAS kao umnožak DRAM vremena ciklusa generatora takta. Treba imati na umu da je ovo polovina brzine podatka prenosa kada se koristi dvostruka brzina prenosa podataka. JEDEC standard PC3200 tajming je 3‐4‐4‐8[5] sa 200 MHz generatorom takta, dok premijum cena visokoh performasi PC3200 DDR DRAM DIMM može da radi na 2‐2‐2‐5 tajmingu.[6]

| PC-3200 (DDR-400) | PC2-6400 (DDR2-800) | PC3-12800 (DDR3-1600) | Opis | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Obično | Brzina | Obično | Brzina | Obično | Brzina | ||||||||

| takt | vreme | takt | vreme | takt | vreme | takt | vreme | takt | vreme | takt | vreme | ||

| tCL | 3 | 15 ns | 2 | 10 ns | 5 | 12.5 ns | 4 | 10 ns | 9 | 11.25 ns | 8 | 10 ns | /CAS nizak na validnom izlazu (ekvivalentno tCAC) |

| tRCD | 4 | 20 ns | 2 | 10 ns | 5 | 12.5 ns | 4 | 10 ns | 9 | 11.25 ns | 8 | 10 ns | /RAS nizak na /CAS nisko vreme |

| tRP | 4 | 20 ns | 2 | 10 ns | 5 | 12.5 ns | 4 | 10 ns | 9 | 11.25 ns | 8 | 10 ns | /RAS precharge vreme (minimalni precharge za aktivno vreme) |

| tRAS | 8 | 40 ns | 5 | 25 ns | 16 | 40 ns | 12 | 30 ns | 27 | 33.75 ns | 24 | 30 ns | Row active time (minimalno aktivno za precharge vreme) |

Poboljšanje u odnosu na 11 godina nije toliko značajno. Minimalno nasumično vreme pristupa je poboljšano od tRAC = 50 ns to tRCD + tCL = 22.5 ns, pa čak i premija 20 ns podvrsta je samo 2,5 puta bolja u odnosu na tipičan slučaj (~ 2,22 puta bolja). CAS kašnjenje je još manje poboljšano, od tCAC = 13 ns 10 ns. Međutim, DDR3 memorija ne postiže 32 puta veći propusni opseg; zbog unutrašnjeg pipelining-a i širokih staza podataka, ona može da ima dve izlazne reči svaka 1.25 ns (1600 Mword/s), dok EDO DRAM može da ima jednu izlaznu reč po tPC = 20 ns (50 Mword/s).

Timing skraćenice

[uredi | uredi izvor]

|

|

Detekcija i korekcija grešaka

[uredi | uredi izvor]Električna ili magnetna interferencija unutar računarskog sistema može da izazove da jedan bit u DRAM-u spontano promeni stanje. Većina jednokratnih ("mekih") grešaka u DRAM čipovima se javlja kao posledica radijacije, uglavnom neutrona iz kosmičkih zraka sekundarno, koji može da menja sadržaj jedne ili više memorijskih ćelija ili da ometa kola koja se koriste za njihovo čitanje/pisanje. Nedavna studija[7] je pokazala da jedan događaj vezan za kosmičku radijaciju dramatično opada sa geometrijom procesa i prethodna zabrinutost nad povećanjem brzine grešaka ćelije su neosnovane.

Ovaj problem može se ublažiti korišćenjem viška memorijskih bitova i memorijskih kontrolera koji koriste ove bitove, obično implementiranih unutar DRAM modula. Ovi dodatni bitovi se koriste da zapamte parnost i da omoguće da se izgubljeni podaci rekonstruišu pomoću koda za izpravljanje grešaka (ECC). Parnost omogućava otkrivanje svih jedno-bitnih grešaka (u stvari, bilo koji neparan broj pogrešnih bita). Najčešći kod za ispravljanje grešaka je SECDED Hamingov kod, omogućava da greška jednog bita bude ispravljena i, u uobičajenoj konfiguraciji, sa dodatnim bitom parnosti, da se detektuje greška dva bita.

ECC sposoban memorijski kontroler koji se korsti u mnogim savremenim računarima obično može da detektuje i ispravi grešku jednog bita u 64-bitnoj reči (jedinica prenosa magistrale), i da detektuje (ali ne i ispravi) grešku dva bita u 64-bitnoj reči. Neki sistemi takođe „ribare“ greške, pisanjem ispravljene verzije nazad u memoriju. BIOS u nekim računarima i operativnim sistemima kao što je Linux, omogućava brojanje detektovanih i ispravljenih memorijskih grešaka; što omogućava identifikaciju i zamenu propalih memorijskih modula.

Nedavne studije daju široku varijaciju stope grešaka preko sedam redova veličine razlike, u rasponu od 10−10−10−17 error/bit·h, otprilije jedna greška bita, po satu, po gigabajtu memorije u jednoj bitnoj greški, po veku, po gigabajtu memorije.[7][8][9] Schroeder 2009 studija prijavila 32% šansi da će računar u svojoj studiji patiti od najmanje jedne ispravljive greške godišnje, a prižio dokaze da većina ovakvih grešaka su isprekidano teške nego meko greške. 2010 studija Rochester University je takođe dala dokaze da znatan deo emorijskih grešaka je isprekidana tvrda greška.[10] Studije velikog obima na ne-ECC RAM u računarima i laptopovima sugeriše da neopažene memorijske greške čine znatan deo memorijskih kvarova: sudija govori da je 1 u 1700 šansi za 1,5% testirane memorije (ekstrapolacijom na približeno 26% šansi za celu memoriju) da bi računar imao memorijsku greške na 8 meseci.[11]

Pakovanje

[uredi | uredi izvor]Iz ekenomskih razloga, velike (glavne) memorije koje se nalaze u ličnim računarima, radnim stanicama, i ne-ručnim igračkim konzolama (kao što su PlayStation i Xbox) obično se sadrže dinamički RAM (DRAM). Ostali delovi računara, kao što su keš memorije i bafer podaci na tvrdim diskovima, obično koriste statički RAM (SRAM).

Opšti DRAM formati

[uredi | uredi izvor]Dinamička memorija sa slučajnim pristupom se proizvodi kao integrisano kolo (IC) zalepljeno i montirano u plastična pakovanja sa metalnim pinovima za povezivanje na kontrolne signale i magistrale. Rana korišćenja pojedinačnih DRAM IC su obično bila ili direktno instaliranje na matičnu ploču ili na ISA kartice za proširenje; kasnije su bili sastvljeni od više-čipnog plug-in modula (DIMM, SIMM, itd.). Neke standardne vrste modula su:

- DRAM čip (integrisano kolo ili IC)

- Dual in-line Package (DIP)

- DRAM (memorijski) moduli

- Single In-line Pin Package (SIPP)

- Single In-line Memory Module (SIMM)

- Dual In-line Memory Module (DIMM)

- Rambus In-line Memory Module (RIMM), tehnički je DIMM ali se zove RIMM zbog slota.

- Small outline DIMM (SO-DIMM), oko polovine redovnih DIMM-a, uglavnom se koriste u notebook-ovima, small footprint PCs (računar sa relativno malim dimenzijama - kao što je Mini-ITX matična ploča), nadogradivim kancelarijskim štampačima i mrežnom hardveru poput rutera. Dolaze u verzijama sa:

- 72-pin (32-bit)

- 144-pin (64-bit) koristi se za SDRAM

- 200-pin (72-bit) koristi se za DDR SDRAM i DDR2 SDRAM

- 204-pin (64-bit) koristi se za DDR3 SDRAM

- Small outline RIMM (SO-RIMM). Manja verzija RIMM-a, koriste se u laptopovima. Tehnički ona je SO-DIMM ali se zove SO-RIMM zbog svog slota.

- Naslagani u relaciji sa ne-naslaganim RAM modulima

- Naslagani RAM moduli sadrže dva ili više RAM čipa naslaganih jedan na drugi. Ovo omogućava da veliki moduli budu proizvedeni korišćenjem jeftinijeg manje gustine wafer-a (wafer: takođe nazivan slice ili substrate je tanko parče poluprovodničkog materijala, kao što je kristal silicijuma, koji se koristi za izradu integrisanih kola i drugih mikrouređaja). Naslagani čip moduli koriste više snage, i imaju tendenciju da rade toplije nego ne-naslagani moduli. Naslagani moduli mogu biti napravljeni korišćenjem starih TSOP ili novih BGA stil IC čipova.

Uobičajeni DRAM moduli

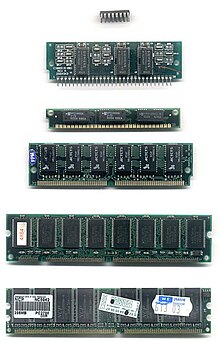

[uredi | uredi izvor]Uobičajeni DRAM paketi ilustrovani desno, od vrha do dna, su:

- DIP 16-pin (DRAM čip, obično pre-fast režim strane DRAM (FPRAM))

- SIPP 30-pin (obično FPRAM)

- SIMM 30-pin (obično FPRAM)

- SIMM 72-pin (često prošireni podaci od DRAM (EDO DRAM) ali FPRAM nije upbičajen)

- DIMM 168-pin (SDRAM)

- DIMM 184-pin (DDR SDRAM)

- RIMM 184-pin (RDRAM) nije prikazan

- DIMM 240-pin (DDR2 SDRAM i DDR3 SDRAM) nije prikazan

Veličina memorije DRAM modula

[uredi | uredi izvor]Tačan broj bajtova u jednom DRAM modulu je uvek integral snage od dvojke (stepen dvojke). 512 MB (kao što je označeno na modulu) SDRAM DIMM, zapravo sadrži 512 MiB (mebibajtova) = 512 × 220 bajtova = 229 bajtova = tačno 536.870.912 bajtova), a može biti sastavljen od 8 ili 9 SDRAM čipova, od kojih svaki sadrži 512 Mib (mebibitova) kapaciteta, i svaki od njih doprinosi 8 bitova na DIMM-ovoj 64- ili 72-bitnoj širini. Za poređenje, 2 GB SDRAM modul sadrži 2 GiB (gigibajta) = 2 × 230 bajtova = 231 bajtova = tačno 2.147.483,648 bajta memorije. Modul obično ima 8 SDRAM čipova od kojih je svaki 256 MiB.

Verzije

[uredi | uredi izvor]Dok su osnovna DRAM ćelija i niz zadržali istu osnovnu strukturu (i performanse) tokom mnogo godina, bilo je mnogo različitih interfejsa za komunikaciju sa DRAM čipovima. Kada neko govori o "DRAM vrstama“, to se generalno odnosi na interfejs koji se koristi.

Asinhroni DRAM

[uredi | uredi izvor]Asinhroni DRAM čip ima veze napajanja, nekoliko adresnih ulaza (obično 12), i nekoliko (obično jedan ili četiri) dvosmernih linija podataka. Postoje četiri nisko-aktivna kontrolna signala:

- /RAS, Row Address Strobe. Adresni ulazi su zarobljeni na silaznoj ivici /RAS-a, i izabere red koji treba da se otvori. Red se održava otvorenim sve dok je /RAS nizak

- /CAS, Column Address Strobe. Adresni ulazi su zarobljeni na silaznoj ivici /CAS-a, i izbor kolone iz trenutno otvorenog reda da čita ili piše.

- /WE, Write Enable. Ovaj signal određuje da li je silazna ivica /CAS čita (ako je visoka) ili piše (ako je niska). Ako je niska, ulazni podaci su takođe zarobljneni na silizanoj ivici /CAS.

- /OE, Output Enable. To je dodantni signal koji kontroliše izlaz na pinovima podataka U/I. Pinovi podataka su vođeni DRAM čipom ako su /RAS i /CAS niski, /WE je visok, i /OE nizak. U mnogim aplikacijama, /OE može biti trajno povezan kao nizak (izlaz je uvek omogućen), ali to može biti korisno kada se povezuje više memorijskih čipova paralelno.

Ovaj interfejs omogućava direktnu kontrolu internog tajmingu. Kada je /RAS nizak, sa /CAS cilkus ne sme da se vrše pokušaji sve dok sense amplifiers ne oseti memorijsko stanje, i /RAS nesme da bude vraćen na visoko sve dok se ćelije za skladištenje ne osveže. Kada je /RAS visoko, on mora biti zadržan visoko dovoljno dugo da se završi prethodno napajanje.

Iako je RAM asinhron, signali se obično generišu pomoću meorijskog kontrolera generatora takta, koji ograničava njihovo vreme množenja ciklusa generatora takta kontrolera.

RAS Only Refresh (ROR)

[uredi | uredi izvor]Klasični asinhroni DRAM se osvežava otvaranjem svakog reda opet.

Ciklus osvežavanja se distribuiše tokom celog intervala osveženje na takav način da se svi redovi osveže u traženom intervalu. Pri osvežavanju jednog reda memorijskog niza koji koristi /RAS Only Refresh, sledeći koraci moraju da se jave:

- Adresa reda koja treba da se osveži mora da se preda ulaznim adresnim pinovima

- /RAS mora da se prebaci sa visokog na nizak. /CAS mora ostati visok.

- Na kraju potrebne količine vremena, /RAS mora da se vrati na visoko.

Omo može da se uradi pomoću snabdevanja reda adrese i pulsiranjem /RAS-a nisko; za to nije neophodno da se izvrši bilo kakav /CAS ciklus. Eksterni brojač je potreban da opet vrši iteraciju kroz redove adresa.[12]

CAS pre RAS osveženja (CBR)

[uredi | uredi izvor]Zbog praktičnosti, brojač je brzo ugrađen u sam RAM čip. Ako je /CAS linija dovedena nisko pre /RAS (obično u nelegalnim radu), onda DRAM ignoriše adrese ulaza i koristi unutrašnji brojač da izabere red koji da otvori. Ovo je poznato kao /CAS-pre-/RAS (CBR) osveženje. Prethodno naelektrisanje kola se isključuje.

Ovo je postao standardni oblik osvežavanja za asinhroni DRAM, i to je samo jedan oblik koji se generalno koristi sa SDRAM-om.

Skriveno osvežavanje

[uredi | uredi izvor]S obzirom na podršku CAS-pre-RAS osveženja, moguć je da deassert (nizak logički izlaz) /RAS dok držimo /CAS nisko da bi se održali izlazni podaci. Ako se /RAS ponovo potvrdi, ovo obavlja CBR cikluse osveženja dok DRAM izlazi ostaju validni. Pošto se izlazni podaci ne prekidaju, ovo je poznato kao „skriveo osvežavanje“.[13]

Video DRAM (VRAM)

[uredi | uredi izvor]VRAM je dual-ported varijanta DRAM-a koja je nekada bio najčešće korišćena za skladištenje frejm-bafera u nekim grafičkim adapterima.

Window DRAM (WRAM)

[uredi | uredi izvor]WRAM je varijanta VRAM-a koji se nekada koristio u grafičkim adapterima kao što su Matrox Millenium i ATI 3D Rage Pro. WRAM je dizaniran da radi bolje i košta manje nego VRAM. WRAM nudi i do 25% veći propusni opseg nego VRAM i ubrzanje koje obično koristi grafičke operacije kao što su tekst crtanje i blok popune.[14]

Fast page mode DRAM (FPM DRAM)

[uredi | uredi izvor]Fast page mode (brzi mod stranice) DRAM-a se takođe zove FPM DRAM, FPRAM, Page mode DRAM, Fast page mode memory, ili Page mode memory.

U modu stranice, red DRAM-a može se držati „otvorenim“ držanjem /RAS niskim dok izvršava više čitanja ili pisanja sa odvojenim pulsevima /CAS-a tako da uzastopna čitanja ili pisanja u redu ne trpe odlaganje prethodnog napajanja i pristupa redu. Ovo povećava performanse sistema kada rafalno čita ili piše podatke.

Statička kolona je varijanta moda stranice u kojoj adresa kolone ne treba da se čuva u, nego, ulazna adresa može da se promeni sa /CAS-om zadržanim nisko, a izlaz podataka će biti ažuriran u skladu sa nekoliko nanosekundi kasnije.

Nibble mode je još jedana varijanta u kojoj četiri uzastopne lokacije u oviru reda mogu biti pristupne sa četiri uzastopna impulsa /CAS-a. Razlika od normalnog režima stranice je ta da se adresni ulazi ne koriste za druge kroz četiri /CAS ivice; oni su generisani interno počev od adrese donošenja prvih /CAS ivica.

Extended data out DRAM (EDO DRAM)

EDO DRAM, ponekad nazivaju Hyper Page Mode omogućen DRAM, je sličan Fast Page Mode DRAM-u sa dodatnim funkcijama da novi pristup ciklusu može biti pokrenut uz zadržavanje izlaza podataka prethodnog aktivnog ciklusa. Prvobitno proizveden u Edo, Japan, EDO je bakronim koji je skovao pronalazač, mladi Kunihiko Kodaira. Ova nova metoda ciklusa omogućava određenu količinu preklapanja u radu (protočna obrada), što omogućava nešto bolje performanse. On je bio 5% brži od FPM DRAM-a, koga je počeo zamnjivati 1995. godine, kada je Intel predstavio 430FX čipset koji podržava EDO DRAM.

Da budemo precizni, EDO DRAM počinje izlaz podataka na silaznoj ivici /CAS-a, ali ne sprečava izlaz kada /CAS ponovo raste. On održava izlaz važećim (tako produžava vreme izlaza podataka) sve dok ili /RAS deasserted, ili nova /CAS silazna ivica izabere drugu adresu kolone.

Jedno-ciklusni EDO ima mogućnost da izvrši kompletanu memorijsku transakciju u jednom ciklusu generatora takta. Inače, svaki sekvencijalni pristup RAM-u u okviru iste stranice traje dva ciklusa generatora takta umesto tri, kada je jednom već izabrana stranica. EDO performanse i mogućnosti dozvoljavaju da pomalo zameni ranije spori L2 keš u PC. On je stvorio priliku da se smanji ogroman gubitak performansi sa L2 kešom, čineći sisteme jeftinijim pri izgradnji. Ovo je takođe dobro za notebooks, zbog problema sa njihovim ograničenjem form factor, i životom baterije. EDO sa L2 kešom bio je osetno brži od starije FPM/L2 kombinacije.

Jedno-ciklusni EDO DRAM postao je veoma popularan za video kartice krajem 1990. godina. Bio je veoma jeftin, a ipak skoro isto efikasan za obavljanje kao daleko skuplji VRAM.

Dosta opreme koje je uzeo 72-pinski SIMM mogli su da koriste FPM ili EDO. Problemi su mogući, posebno kada se mešaju FPM or EDO. Rani Hewlett-Packard štampači su imali ugrađen FPM RAM; neki, ali ne svi, modeli su radili ako su dodati dodatni EDO SIMM-ovi.[15]

Rafalni EDO DRAM (BEDO DRAM)

[uredi | uredi izvor]Evolucija EDO DRAM, Rafalnog EDO DRAM, mogla je da obradi četiri memorijske adrese u jednom rafalu, za maksimum od 5-1-1-1, koji čuva dodatna tri ciklusa preko optimalnog dizajna EDO memorije. To je učinjeno dodavanjem brojača adrese na čipu da prati trag sledeće adrese. BEDO je takođe dodao stanje protočne obrade omogućavajući da se ciklus pristupa stranici podeli u dve komponente. Tokom operacije memorijskog čitanja, prva komponenta pristupa podacima iz memorijskog niza na izlaznom stanju (drugi leč). Druga komponenta dovodi magistralu podataka sa ovog leča na odgovarajući logički nivo. Pošto su podaci već u izlaznom baferu, postiže se brže vreme pristupa (i do 50% za velike blokove podataka) nego sa tradicionalnim EDO-m.

Iako je BEDO DRAM pokazao dodatnu optimizaciju na EDO, vremenom on je bio dostupan na tržištu gde je napravio je značajnu investiciju prema sinhronom DRAM-u ili SDRAM-u [1][mrtva veza]. Iako je BEDO RAM bio superiorniji u odnosu na SDRAM na neki način, kasnija tehnologija brzo izbacila BEDO.

Multibank DRAM (MDRAM)

[uredi | uredi izvor]Multibank DRAM primenjuje tehniku preplitanja za glavnu memoriju do keš memorije niva dva da obezbedi jeftiniju i bržu alternativu za SRAM. Čip deli svoje memorijske kapacitete u male blokove od 256 kB i omogućava rad na dve različite banke u jednom ciklusu.

Ova memorija se prvenstveno koristila u grafičkim karticama sa Tseng Labs ET6x00 čipsetom, napravljena od MoSys. Ploče zasnovane na ovom čipsetu često su koristile neobičnu konfiguraciju veličine RAM-a od 2.25 MB, zahvaljujući sposobnosti MDRAM-a da lakše bude implementiran u različitim veličinama. Ova veličina od 2.25 MB omogućava 24-bitnu boju na rezoluciji od 1024h768, veoma popularna postavka ekrana u vreme kartica.

Sinhroni grafički RAM (SGRAM)

[uredi | uredi izvor]

SGRAM je specijalizovana forma SDRAM za grafičke adaptere. Ona dodaje funkcije kao što su bit maskiranje (pisanje na određenoj bit ravni bez uticaja na drugu) i blok pisanje (punjenje bloka meorije sa jednom bojom). Za razliku od VRAM i WRAM, SGRAM je single-ported. Međutim, on može da otvori dve stranice istovremeno, što simulira dual-port prirodu drugih VRAM modula.

Sinhroni dinamički RAM (SDRAM)

[uredi | uredi izvor]SDRAM značajno revidira asinhroni memorijski interfejs, dodajući generatorsku takt (i generatorski takt omogućava) liniju. Svi ostali signali se primaju na uzlaznu ivicu generatorskog takta.

/RAS i /CAS ulazi više ne deluju duže kao farovi, ali su umesto toga, zajedno sa /WE, deo 3-bitne komande:

| /CS | /RAS | /CAS | /WE | Adresa | Komanda |

|---|---|---|---|---|---|

| H | x | x | x | x | Inhibicija komande (nema operacija) |

| L | H | H | H | x | Nema operacija |

| L | H | H | L | x | Rafalni prekid: zaustaviti rafalno čitanje ili pisanje u toku |

| L | H | L | H | kolona | Čitati sa trenutno aktivnog reda |

| L | H | L | L | kolona | Pisati u trenutno aktivni red |

| L | L | H | H | red | Aktivirati red za čitanje i pisanje |

| L | L | H | L | x | Prethodno napunjen (deaktivirari) trenutni red |

| L | L | L | H | x | Automatsko osvežavanje: Osvežiti jedan red svake banke, korišćenjem unutrašnjeg brojača |

| L | L | L | L | režim | Učitavanje više registara: Adresna magistrala specifikuje DRAM operacije moda |

/OE linijska funkcije je proširena po bajtu na "DQM" signalu, koji kontroliše ulaz podataka (pisanja) pored izlaza za podatke (čitanje). Ovo omogućava DRAM čipu da bude širi od 8 bitova, dok još uvek podržava pisanje bajt-granulacije.

Mnogi vremenski parametri su ostali pod kontrolom DRAM kontrolera. Na primer, minimalno vreme mora proći između aktiviranja reda i komande čitanja ili pisanja. Jedan važan parametar mora biti programiran u samom SDRAM čipu, a to je CAS kašnjenje. To je broj ciklusa generatora takta dozvoljenih za unutrašnje operacije između komande čitanja i prve reči podatka koja se javlja na magistrali podataka. Komanda "Load mode register" se koristi da prenese ovu vrednost SDRAM čipu. Ostali parametri su podesive dužine rafalnog čitanja i pisanja, odnosno broja reči prenetih po komandi pisanja ili čitanja.

Najznačajnija promena, glavni razlog zašto je SDRAM zamenio asinhroni RAM, je podrška za više unutrašnjih banaka unutar DRAM čipa. Koristeći nekoliko bitova „bančine adrese“ koja prati svaku komandu, druga banka može da se aktivira i započne čitanje podataka dok je čitanje prve banke još uvek u toku. Pomoću naizmeničnih banaka, SDRAM uređaj može da zadrži magistralne podatke stalno zauzetim, na način koji asinhroni DRAM ne mogu.

Jednostruka brzina prenosa (SDR)

[uredi | uredi izvor]Jednostruka brzina prenosa SDRAM (ponekad poznat kao SDR) je asinhroni oblik DRAM-a.

Dvostruka brzina prenosa (DDR)

[uredi | uredi izvor]Dvostruka brzina prenosa SDRAM ('DDR) je kasnije razvijena od SDRAM, koristila se u PC memoriji početkom 2000. godini. Naknadne verzije su numerisane sekvencijalno (DDR2, DDR3, itd.). DDR SDRAM interno obavlja duplu širinu pristupa u generatorskom taktu, i koristi dvostruke brzine prenosa interfejsa da prenese polovinu na svaku ivicu generatorskog takta. DDR2 i DDR3 su povećali ovaj faktor na 4h i 8h isporučujuću rafalno 4-reči i 8-reči tokom 2 i 4 ciklusa generatorskog takta. Interna brzina pristupa je uglavnom nepromenjena (200 miliona u sekundi za DDR-400, DDR2-800 i DDR3-1600 memorije), ali svaki pristup prenosi više podataka.

Direktan rambus DRAM (DRDRAM)

[uredi | uredi izvor]Direktan rambus DRAM (DRDRAM) je razvio Rambus.

Pseudostatic RAM (PSRAM)

[uredi | uredi izvor]PSRAM ili PSDRAM je dimični RAM sa ugrađenim osvežavanjem i kolom kontrole adrese da bi se slično ponašali kao statički RAM (SRAM). On kombinuje visoku gustinu DRAM-a sa lakoćom korišćenja istinskog SRAM-a. PSRAM (napravljen od strane Numonyx) se koristi u Apple iPhone i drugim ugrađenim sistemima kao XFlar Platform.[16]

Neke DRAM komponente imaju „samo-osvežavajući-režim“. Iako to podrazumeva mnogo iste logike koja je potrebna za pseudo-statičke operacije, ovaj režim je često ekvivalentan sa režimom mirovanja. Predviđen je pre svega da omogući sistemu da suspenduje operacije svog DRAM kontrolera radi uštede energije bez gubitka podatak sačuvanih u DRAM-u, i da ne dozvoliti operacije bez odvojenog DRAM kontrolera kao što je slučaj sa PSRAM-om.

Ugrađena varijanta PSRAM se prodaje od MoSys pod imenom 1T-SRAM. To je tehnički DRAM, ali se ponaša više kao SRAM. Koristi se u Nintendo Gamecube i Wii konzoli.

Smanjeno kašnjenje DRAM (RLDRAM)

[uredi | uredi izvor]Smanjeno kašnjenje DRAM-a je visoka performansa dvostruke brzine prenosa (DDR) SDRAM koji kombinuje brzi, slučajni pristup sa visokim propusnim opsegom, uglavnom namenjen umrežavanju i keširanju aplikacija

1T DRAM

[uredi | uredi izvor]Za razliku od svih ostalih varijanti opisanih u ovom odeljku ovog članka, 1T DRAM je drugačiji način izgradnje osnovne DRAM bit ćelije. 1T DRAM je „kapacitatorska“ bit ćelija dizajnirana da skladišti podatke u parazitskom telu kondenzatora koji je satavni deo silikona, na izolovani (SOI) tranzistor. Posmatranje smetnje u logičkom dizajnu, ovaj efekat plutajućeg tela može se koristiti za skladištenje podataka. Iako je još potrebno osvežavanje, čita se bez razaranja; napunjena skladišta izazivaju merljiv pomak u naponu praga tranzisotra.[17]

Postoji nekoliko tipova 1T DRAM dram memorije: komercijalizovan Z-RAM od Innovative Silicon, TTRAM od Renesas i A-RAM od UGR/CNRS konzorcijuma.

Klasična jedan-tranzistor/jedan-kapacitator (1T/1C) DRAM ćelija se takođe ponekad naziva kao "1T DRAM", naročito u poređenju 3T i 4T DRAM koji je zamenjen 1970. godine.

Sigurnost

[uredi | uredi izvor]Iako dinamička memorija je definisana i garantuje da čuva svoj sadržaj kada se snabdeva sa napajanjem i kada se osvežava u kratkim vremenskim intervalima (najčešće 64 ms), memorijska ćelija kondenzatora često zadržava svoju vrednost znatno duže, posebno na niskim temperaturama. Pod nekim uslovima većina podataka na DRAM-u može biti vraćena čak ako on nije bio osveživan nekoliko minuta.[18]

Ovo svojstvo može da se koristi da se zaobiđe bezbednost i oporave podaci uskladišteni u memoriji i pretpostalja se da je uništen u nestajanju struje brzim restartovanjem računara i dampovanjem sadržaja RAM-a, ili hlađenjem čipa i njihovim prebacivanjem na drugi računar. Takav napad je demonstrirao zaobilaženje popularne enkripcije disk sistema, kao što je otvoreni kod TrueCrypt, Microsoft's BitLocker Drive Encryption, i Eplov FileVault.[traži se izvor] Ova vrsta napada na računar se često naziva hladno pokretanje napada.

Vidi još

[uredi | uredi izvor]Reference

[uredi | uredi izvor]- ^ Copeland 2006, str. 301

- ^ Spec Sheet for Toshiba "TOSCAL" BC-1411

- ^ Toshiba "Toscal" BC-1411 Desktop Calculator (The introduction date is listed here as November 1965, but this is a year too early and appears to be a typographical error.)

- ^ „Micron 4 Meg x 4 EDO DRAM data sheet” (PDF). Arhivirano iz originala (PDF) 27. 09. 2007. g. Pristupljeno 19. 12. 2013.

- ^ cmx1024-3200.ai

- ^ https://web.archive.org/web/20040529091249/http://www.corsairmemory.com/corsair/products/specs/twinx1024-3200xl.pdf

- ^ a b Borucki, "Comparison of Accelerated DRAM Soft Error Rates Measured at Component and System Level", 46th Annual International Reliability Physics Symposium, Phoenix, (2008). str. 482–487

- ^ http://www.cs.toronto.edu/~bianca/papers/sigmetrics09.pdf

- ^ „A Memory Soft Error Measurement on Production Systems[[Kategorija:Botovski naslovi]]”. Arhivirano iz originala 14. 02. 2017. g. Pristupljeno 19. 12. 2013. Sukob URL—vikiveza (pomoć)

- ^ Li, Huang; Shen, Chu (2010). „"A Realistic Evaluation of Memory Hardware Errors and Software System Susceptibility". Usenix Annual Tech Conference 2010” (PDF).

- ^ „Cycles, cells and platters: an empirical analysis of hardware failures on a million consumer PCs. Proceedings of the sixth conference on Computer systems (EuroSys '11).” (PDF). 2011. str. 343—356.

- ^ „Arhivirana kopija” (PDF). Arhivirano iz originala (PDF) 29. 08. 2017. g. Pristupljeno 19. 12. 2013.

- ^ Various Methods of DRAM Refresh Arhivirano na sajtu Wayback Machine (3. oktobar 2011) Micron Technical Note TN-04-30

- ^ The PC Guide, definition of WRAM.

- ^ Page on memory upgrades for HP printers

- ^ „EE Times teardown of iPhone 3G”. Arhivirano iz originala 22. 01. 2013. g. Pristupljeno 19. 12. 2013.

- ^ Sallese, Jean-Michel (20. 6. 2002). „Principles of the 1T Dynamic Access Memory Concept on SOI” (PDF). MOS Modeling and Parameter Extraction Group Meeting. Wroclaw, Poland. Arhivirano iz originala (PDF) 22. 3. 2003. g. Pristupljeno 7. 10. 2007.

- ^ Scheick, Leif Z.; Guertin, Steven M.; Swift, Gary M. (2000). „Analysis of radiation effects on individual DRAM cells”. IEEE Trans. on Nuclear Science. 47 (6): 2534—2538. ISSN 0018-9499. doi:10.1109/23.903804. Pristupljeno 8. 8. 2013.

Literatura

[uredi | uredi izvor]- Copeland, Jack B. (2006). Colossus: The Secrets of Bletchley Park's Codebreaking Computers. Oxford: Oxford University Press. str. 301.